Loading…

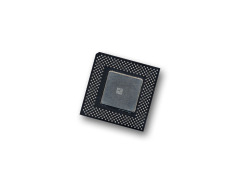

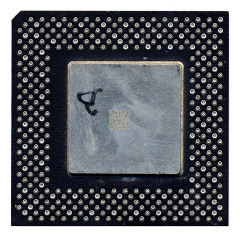

Celeron 500 MHz ES

Week 20, Year 1999FV524RX500 / 128 QD27ES / MALAY / L920500Q-1255 '98

An early sample of the 66-MHz FSB Celeron built with the Mendocino, 0.25 µm core, the Celeron 500. It comes with 128 KB of L2 cache and was announced in August, 2nd 1999 by Intel. This sample was built in May '99.